[menuju akhir]

1. Tujuan [kembali]

- Dapat mengetahui apa yang dimakud dengan Depletion-Type Mosfets

- Dapat mengatahui rumus-rumus yang digunakan dalam Depletion-Type Mosfets

- Mampu memahami rangkaian-rangkaian yang dibuat pada aplikasi proteus

2. Komponen [kembali]

a. Transistor, sebuah komponen elektronika yang digunakan untuk penguat, sebagai sirkuit pemutus,

sebagai penyambung, sebagai stabilitas tegangan, dan modulasi sinyal.

b. Kapasitor, adalah komponen elektronika yang berfungsi menyimpan muatan listrik dalam jangka

waktu tertentu.

c. Ground, titik yang dianggap sebagai titik kembalinya arus listrik arus searah atau titik kembalinya

sinyal bolak balik atau titik patokan (referensi) dari berbagai titik tegangan yang berfungsi sebagai

pengaman ketika terjadi kebocoran arus listrik.

3. Ringkasan [kembali]

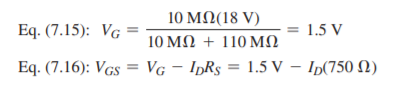

Kemiripan tampilan antara kurva transfer JFET dan tipe deplesi MOSFET memungkinkan analisis yang serupa dari masing-masing domain dc. Perbedaan utama antara keduanya adalah fakta bahwa MOSFET tipe deplesi mengizinkan titik operasi dengan nilai positif V GS dan level I D yang melebihi I DSS . Faktanya, untuk semua konfigurasi yang dibahas sejauh ini, analisisnya sama jika JFET diganti dengan MOSFET tipe deplesi.

Satu-satunya bagian analisis yang tidak terdefinisi adalah bagaimana memplot persamaan Shockley menjadi positif nilai V GS .

4. Example [kembali]

- Untuk MOSFET tipe penipisan saluran-n pada Gambar 7.30, tentukan:

A. IDQ dan VGSQ.

B. V DS .Jawab:

a. Untuk karakteristik transfer, titik plot ditentukan oleh ID = IDSS>4 = 6 mA>4 = 1,5 mA

dan VGS = VP>2 = -3 V>2 = -1,5 V. Mempertimbangkan tingkat VP dan fakta bahwa

Persamaan Shockley mendefinisikan kurva yang naik lebih cepat saat V GS menjadi lebih positif,

titik plot akan ditentukan pada VGS = +1 V. Mengganti ke hasil persamaan Shockley

Kurva transfer yang dihasilkan tampak pada Gambar 7.31. Melanjutkan seperti yang dijelaskan untuk JFET, kita punyaAtur ID = 0 mA maka akan menghasilkan,

Atur VGS = 0 V menghasilkan,

Titik-titik plot dan garis bias yang dihasilkan tampak pada Gambar 7.31. Operasi yang dihasilkan

poin diberikan oleh,

2.Ulangi Contoh 1 dengan RS = 150 . jawab:

a.Titik-titik plot untuk kurva transfer sama seperti yang ditunjukkan pada Gambar 7.32. Untuk garis bias,

VGS = VG - IDRS = 1.5 V - ID(150 )

Atur ID = 0 mA menghasilkan

VGS = 1,5 V

Atur VGS = 0 V menghasilkan

Garis bias disertakan pada Gambar 7.32. Perhatikan dalam hal ini bahwa hasil titik diam

di saluran pembuangan yang melebihi I DSS , dengan nilai positif untuk V GS . Hasilnya adalah

b. Persamaan. (7.19):

3. Tentukan yang berikut ini untuk jaringan pada Gambar 7.33 :

a. IDQ dan VGSQ.

b. VD.

Jawab :

a. Konfigurasi self-bias menghasilkan

seperti yang diperoleh untuk konfigurasi JFET, menetapkan fakta bahwa V GS harus kurang dari

0 V. Oleh karena itu tidak ada persyaratan untuk memplot kurva transfer untuk nilai positif dari

V GS , meski dilakukan pada kesempatan ini untuk melengkapi karakteristik transfer. A

titik plot untuk karakteristik transfer untuk VGS < 0 V adalah

dan untuk VGS > 0 V, karena VP = -8 V, kami akan memilih

Kurva transfer yang dihasilkan tampak pada Gambar 7.34. Untuk garis bias jaringan, di

VGS = 0 V, ID = 0 mA. Memilih VGS = -6 V memberi

Q -point yang dihasilkan diberikan oleh

5. Problem [kembali]

1. Untuk konfigurasi self-bias pada Gambar 7.92, tentukan:

a. IDQ dan VGSQ.

b. VDS dan VD .

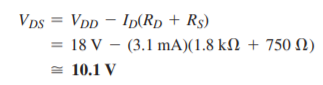

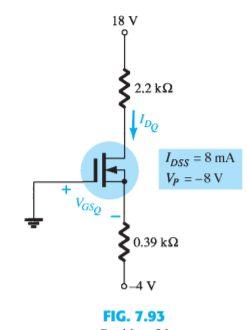

2.Untuk jaringan pada Gambar 7.93, tentukan:

a. IDQ dan VGSQ.

b. VDS dan VS .

6. Soal Pilihan Ganda [kembali]

7. Rangkaian Proteus [kembali]

8. Video [kembali]

9. Download File [kembali]

[menuju awal]

Komentar

Posting Komentar