Tugas Pendahuluan 2 Modul 4

Percobaan 3 Kondisi 5

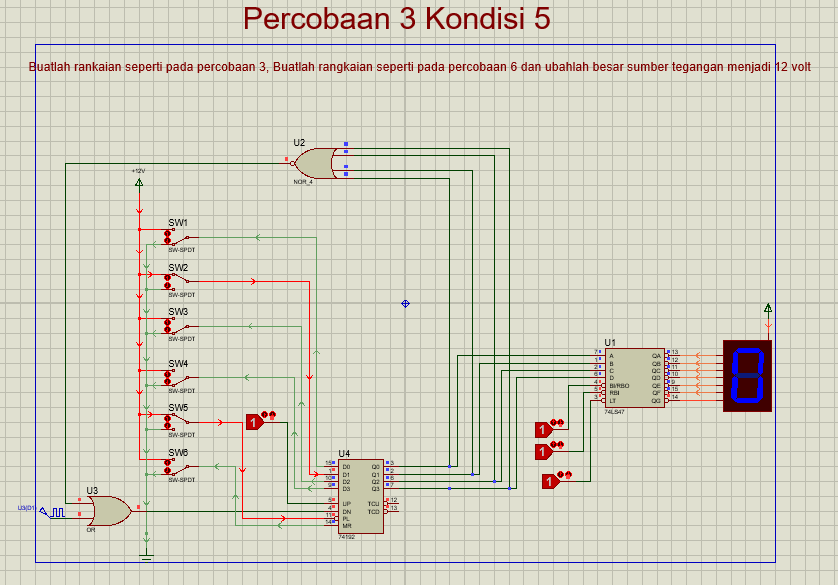

Buatlah rankaian seperti pada percobaan 3, Buatlah rangkaian seperti pada percobaan 6 dan ubahlah besar sumber tegangan menjadi 12 volt

2. Gambar Rangkaian Simulasi[Kembali]

Percobaan 3 Kondisi 5

Pada rangkai terdapat IC 74192 yang merupakan syncrounus Counter , kemudian ada decoder dan 7-Segmend dengan common Katoda karena dihubungkan ke VCC. Terdapat sumber Vcc dihubungkan terhadap switch lalu masuk ke kaki input pada IC 74192. Kaki input D0, D1, D2, D3 akan menjadi output dari masing masing Q0, Q1, Q2 dan Q3. Disini karena semua kaki input dari gerbang logika NOR berlogika 0, maka untuk outputnya berlogika 1 sesuai dengan tabel kebenaran dari gerbag NOR. Kemudian outputnya memasuk kaki input dari gerbang OR yang mana berlogika 1 dan kaki lainnya dihubungkan dengan CLOCK. kemudian masuk ke kaki DN. Dikarenakan kaki DN terhubung dengan sinyal clock maka untuk disini jenis counternya adalah counter down. terdapat juga kaki PL yang merupakan Pload dan kaki MR yang merupakan master reset. Gerbang logika OR dan NOR berfungsi untuk menghentikan counter ketika output sudah bernilai nol.

Kemudian input dari IC 74192 masuk ke kaki A, B, C dan D yang nantinya menjadi output dari masing masing QA, QB, QC dan QD dan ditampilkan melalui seven segment. kaki RBO dan RBI akan mempengaruhi keluaran pada seven segment.

Pada rangkaian terjadi counter Down dari 9 ke 0 kemudian berhenti dio nol karena ada gerbang logika or. Gerbang logika OR dan NOR berfungsi untuk menghentikan counter ketika output sudah bernilai nol.

Rangkaian Percobaan disini

Video Percobaan disini

Komentar

Posting Komentar